ADC signal-to-noise and distortion ratio (SNDR or SiNAD)

Total Harmonic Distortion(THD)

Where V2, V3,...Vn are the magnitude of harmonic distortions. Higher frequency will have less magnitude, which is less than the noise floor or is beyond the bandwidth of interest. Data sheet typically specifies to what order the harmonic distortion has been calculated. For example, up to the fifth harmonic is common.

Signal-to-noise ratio (SNR)

ENOB

For testing ADC, a near full-scale input signal (the preferred input-tone amplitude is -0.5dBFS to -1dBFS) is applied, which avoids the situation of overdriving the quantizer. For the full-scale input, ENOB is expressed:

If the input signal is less than full-scale, like -0.5dBFS (expressed in dB related full scale), the ENOB is expressed:

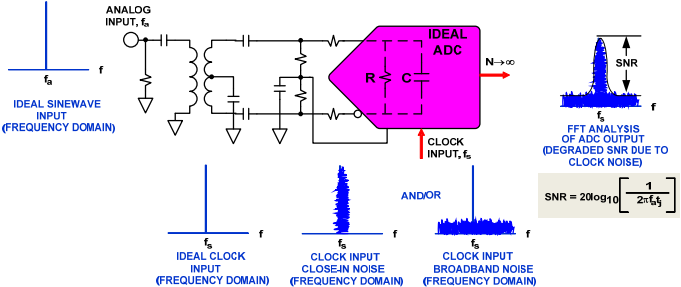

Clock Jitter

High-speed high-resolution ADCs are sensitive to the quality of the clock input. To achieve superior SNR in a high-speed ADC, the RMS clock jitter must be carefully considered, based on the requirements of the applications' input frequency.

|

| Clock jitter limited SNR can be plotted against the analog input frequency for various clock-jitter profiles |

Faster input frequency needs smaller clock jitter to obtain the same SNR. For example, an rms clock jitter of 200fs limits an ADC's SNR performance to no better than 70dB at 250MHz. However, a 1GHz input signal would need an rms clock jitter of 50fs or better to achieve the same SNR performance of 70dB.

No comments:

Post a Comment