Ref: https://en.wikipedia.org/wiki/Display_resolution

"At first, create a dummy directory with the name you want to give your combined library (kind of a kludge, but oh well). Then edit your cds.lib and add 2 lines:

DEFINE <combinedLibName> <pathToDummyDirectoryYouCreatedAbove>

ASSIGN <combinedLibName> COMBINE <lib1> <lib2> ...

These lines need to go after all the lib1, lib2, etc. libraries are defined.

That's it. Now when you open the Library Manager, you'll see your combined library name with a "+" sign next to it. If you click on the combined library name, you'll see all the cells in all the libraries combined. If you click the "+" sign, you can still access the libraries individually as usual. "

[1] Design of an ultra-low power SA-ADC with medium/high resolution and speed written by Andrea Agnes, and et al.

|

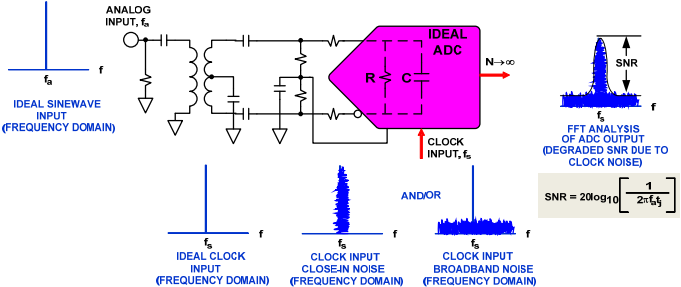

| Clock jitter limited SNR can be plotted against the analog input frequency for various clock-jitter profiles |

| N | ωN/ω1 | |AV(0)| |

|---|---|---|

1

|

1

|

10000

|

2

|

64.36

|

100

|

3

|

236.64

|

21.54

|

4

|

434.98

|

10

|

5

|

611.16

|

6.31

|

10

|

1066.55

|

2.51

|

20

|

1184.87

|

1.58

|

| Noise of capacitor at T=300K | ||

|---|---|---|

| Capacitance (fF) |

sqrt(kT/C) rms noise (uV) |

peak to peak noise (uV) |

| 1 | 2034.698995 | 13429.01337 |

| 10 | 643.4283177 | 4246.626897 |

| 20 | 454.9725266 | 3002.818676 |

| 40 | 321.7141588 | 2123.313448 |

| 50 | 287.7498914 | 1899.149283 |

| 60 | 262.6785107 | 1733.678171 |

| 100 | 203.4698995 | 1342.901337 |

| 120 | 185.7417562 | 1225.895591 |

| 150 | 166.1324773 | 1096.47435 |

| 240 | 131.3392554 | 866.8390854 |

| 1000 | 64.34283177 | 424.6626897 |

| number of bits | 0.5LSB | Time Constant (k) multiplier | Time Constant (k) multiplier |

|---|---|---|---|

| 8 | 0.1953125% | 6.2 | 6.9 |

| 9 | 0.0976563% | 6.9 | 7.6 |

| 10 | 0.0488281% | 7.6 | 8.3 |

| 11 | 0.0244141% | 8.3 | 9.0 |

| 12 | 0.0122070% | 9.0 | 9.7 |

| 14 | 0.0030518% | 10.4 | 11.1 |

| 16 | 0.0007629% | 11.8 | 12.5 |

| 18 | 0.0001907% | 13.2 | 13.9 |

| 20 | 0.0000477% | 14.6 | 15.2 |

| 22 | 0.0000119% | 15.9 | 16.6 |

| 24 | 0.0000030% | 17.3 | 18.0 |

| 1/2 LSB settling accuracy | 1/4 LSB settling accuracy |

~/.mozilla/firefox and look for a folder with a mix of numbers and letters followed by "Default User". In this folder, you will find an invisible file called .parentlock; delete this file and the problem should be fixed.find . -name "*.cdslck"find . -name "*.cdslck" -exec rm -f {} \;envSetVal("auCore.misc" "labelDigits" 'int 5)

editor="gedit"

editor="gedit"

You may also use envSetVal to set the environment. For example, to set the background to white, type the following in the CIW window.;width viva.graphFrame width string "900" ;height viva.graphFrame height string "700" ;background color viva.rectGraph background string "white" ;foreground color viva.rectGraph foreground string "black" ;axis font viva.axis font string "Fixed [Misc],14,-1,5,50,0,0,0,0,0" ;marker font viva.pointMarker font string "Fixed [Misc],14,-1,5,50,0,0,0,0,0" viva.horizMarker font string "Fixed [Misc],14,-1,5,50,0,0,0,0,0" viva.vertMarker font string "Fixed [Misc],14,-1,5,50,0,0,0,0,0" viva.multiDeltaMarker font string "Fixed [Misc],14,-1,5,50,0,0,0,0,0" viva.refPointMarker font string "Fixed [Misc],14,-1,5,50,0,0,0,0,0" ;line thickness viva.trace lineThickness string "thick"

envSetVal(“viva.rectGraph” “background” 'string “white”)

N0 with the name of the device whos operating point you wish to save:save N0:oppointgetData("M0:vdsat" ?result 'dc)).N0:gm). More information about the save command can be found in the spectre documentation or by running spectre -h save at the terminal.