In 2018, over $1B is raised by over 70 LiDAR companies. Analysts from Markets and Markets (www.marketsandmarkets.com) forecast the LiDAR market is going to hit 5,204.8 Million USD and will grow at a CAGR of 25.8% from 2018 to 2022. Therefore, the next five years will be a golden age for the automotive LiDAR market.

Today, let's talk about some basic knowledge about LiDAR.

LiDAR stands for Light Detection and Ranging (sometimes

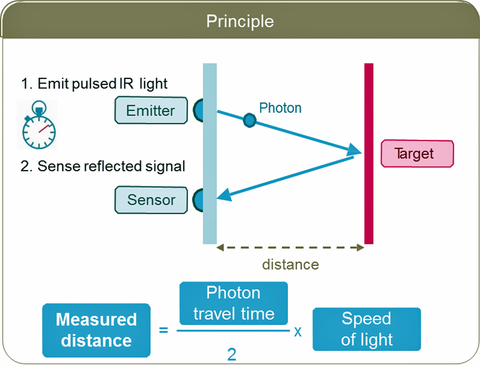

light imaging, detection, and ranging). It is a surveying method that measures a distance to a target by illuminating the target with pulsed laser light and measuring the reflected pulses with a sensor. Differences in laser return times and wavelengths can then be used to make digital 3-D representations of the target.

Applications

LiDAR has broad applications in geodesy, geomatics, archaeology, geography, geology, geomorphology, seismology, forestry, atmospheric physics, laser guidance, airborne laser swath mapping, and laser altimetry. Nowadays, it is also used in control and navigation for some autonomous cars becoming the world-wide favorite topic both in academic and industry.

If you would like to know more about history and general discussions about LiDAR, please visit

LiDAR Wikipedia page.

|

| Image of a rotating LiDAR unit from Renishaw. |

In this article, the automotive LiDAR sensor is talked, especially focusing on receiver part. The recent hot topics and research limitation will also be mentioned. LiDAR sensor is used as assistance system for a driver. The challenge is to ensure that it will function under all possible environmental conditions (temperature, solar radiation, darkness, rain, snow), and above all, recognize objects up to 300 yards away. And of course, all this in large-scale production at the lowest possible cost and smallest dimensions.

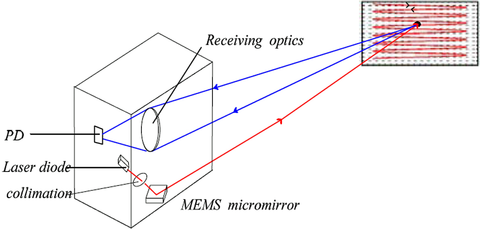

In addition to the transimitter (laser), the system requires a highly sensitive receiver. There are two gnereral trends in the automotive market now: infrared LIDAR systems that with the aid of a MEMS, use a rotating laser, or a solid-state LIDAR.

The receiving system has the task to recongnize the light beams emitted as well as reflected from the object. The detectors must be extremely sensitive and able to measure single photons. Today, the state-of-the-art devices use SPAD technology.

The SPAD cell principle is simple. For the diode with a special geometry, the p-n junction is biased so that a single photon to trigger an avalanche breakdown current in the diode. The resulting sudden rise of the diode current is detected by a corresponding circuit, and then outputs the now digital signal for further processing.

The principle of distance measurement is shown above using an SPAD sensor. The laser at t0 time emits a pulse which is reflected by the obstacle, and after t1 time one (or more) photon reaches the sensor cell. The distance can be determined from the running time.

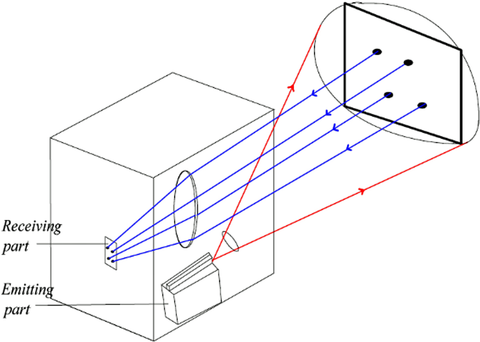

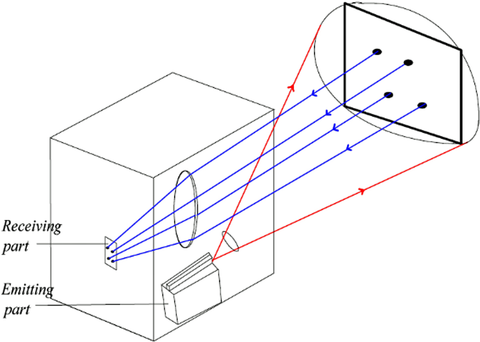

If one or several beams are radiated by rotating mirrors or micro-mechanical systems and there is a correspondingly large pad array of several cells, three-dimension objects can be detected.

|

| Solid state LIDAR system |

|

|

|

|

|

|

|

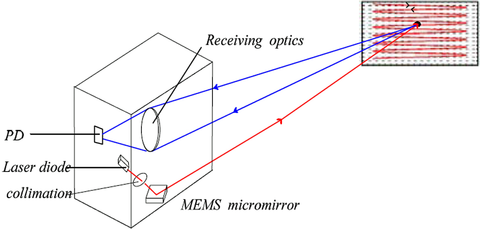

| MEMS-based LIDAR system |

Two common LIDAR systems are shown above. When using micro-mirror based on MEMS technology, the individual laser beam is radiated and reflected in a line shape. The reflected photons are evaluated by a corresponding optics sensor in the SPAD cell. Extreme demands are placed on the mirror system with regard to precision, service life, adjustablity, and reliability.

In this system, several laser diodes (over 100) and an accordingly large receiver array are required. The laser diodes must be equipped with pulse widths in the nanosecond range and with currents of a few amperes, which poses a significant challenge to the semiconductor drivers.

Most LiDAR systems employ infrared rather than visiable radiation. Because electromagnetic radiation's interaction with matter is governed by wavelength, some wavelengths work better for certain applications. Someday microwave (maser) or x-ray (xaser) lasers could be used to build LiDAR systems that can image through a wide variety of materials, greatly enhancing their usefulness.

|

| Block diagram of a ToF LiDAR system (Image courtesy of ISSCC2018) |

Solid-state LiDAR unites are on the market now. As time progresses, their cost will continue to drop and their capabilities will continue to improve. For example, it can be used from electric wheelchair and drones to motorcycles and other mobile plateforms, aside from autonomous cards.